1. 全/低速设备SYNC被定义长度为8位,高速长度定义为32位

全/低速设备SYNC被定义长度为8位(0000 0001),高速长度定义为32位(0000 0000 0000 0000 0000 0000 0000 0001)。 长度不同的根本原因:传输速率与信号完整性。

USB 全/低速(12 Mbps)和高速(480 Mbps)的速率差异巨大,导致对同步信号的要求不同:

- 全低速设备:速率较低,较短的 SYNC(8 bits)即可满足时钟同步需求。

- 高速设备:速率提高 40 倍,需要更长的 SYNC(32 bits)来应对信号衰减和时钟抖动。

注意,这个长度是对发送端的要求。

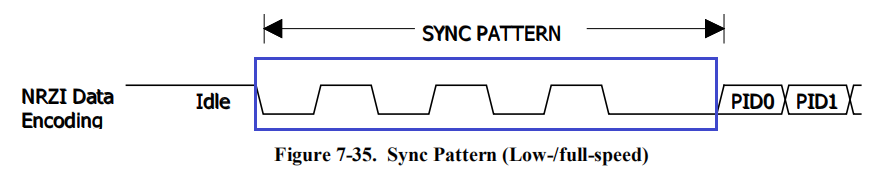

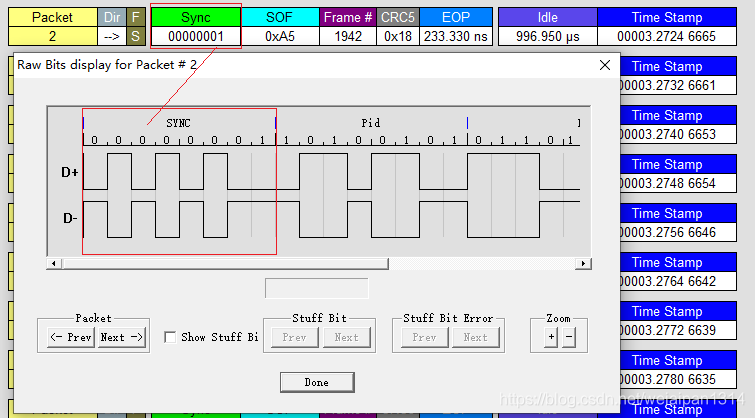

下图是一个全速/低速设备,经过NRZI编码后的波形。SYNC域 8位 中的 最后两位 是一个标记(电平未翻转,即收到数据1),用于标识 SYNC域的结束 和 PID域 的开始。

2. 全速 SYNC:00000001(KJKJKJKK)

设计逻辑:

- 二进制模式:

00000001- 前 7 bits 为

0(交替跳变KJ),最后 1 bit 为1(连续KK表示结束)。

- 前 7 bits 为

- 电平表现:

K J K J K J K KK(低电平),J(高电平),通过 6 次跳变(KJ×3)实现同步。

- 作用:

- 提供足够的跳变边缘(6次)供接收方锁定时钟相位。

- 最后

KK作为同步结束标志,与后续 PID 字段隔离。

为什么是 8 bits?

- 全速信号质量较好,较短的 SYNC 即可稳定同步。

- 协议设计时权衡效率与可靠性。

3. 高速 SYNC:00000000000000000000000000000001(JK*15 + K)

设计逻辑:

- 二进制模式:

00000000000000000000000000000001- 前 31 bits 为

0(跳变JK),后 1 bits 为1(K)。

- 前 31 bits 为

- 电平表现:

J K J ... K K

为什么是 32 bits?

高频信号挑战:

- 高速传输易受信号衰减、反射和噪声干扰,需要更长的同步序列稳定时钟。

时钟恢复需求:

兼容性与鲁棒性:

- 长 SYNC 可容忍更多信号失真,确保高速数据可靠解析。

4. 技术背景补充

NRZI 编码与位填充:

SYNC 的跳变模式需配合 NRZI 编码(跳变=0,无跳变=1)。长串0产生连续跳变(KJ),而1会导致电平保持(可能失去同步,因此需要位填充)。协议演进:

USB 1.x(全速)的 SYNC 设计在 USB 2.0(高速)中扩展,以应对更高频段的信号衰减问题。

5. 实际意义

- 全速设备:短 SYNC 降低协议开销,适合低速场景。

- 高速设备:长 SYNC 是 480 Mbps 传输的基础保障,确保数据包正确解析。

这种差异体现了 USB 协议在不同速率下的工程权衡:速度越高,同步信号需要越长的”训练序列”以对抗物理层干扰。

状态:

需完善 高速 SYNC 部分 关于最后2位是否补充K ?